2.2 Verilog 组合逻辑 UDP

精华

小牛编辑

146浏览

2023-03-14

与非门实例

组合逻辑 UDP 中,状态表规定了不同的输入组合和相对应的输出值,没有指定的任意组合输出值为 x。

一个简单的与非门 UDP 可以表示如下:

primitive nand_my

(out

, a

, b

)

;

output out ;

input a , b ;

table

//a b : out ;

0 0 : 1 ;

0 1 : 1 ;

1 0 : 1 ;

1 1 : 0 ;

endtable

endprimitive

output out ;

input a , b ;

table

//a b : out ;

0 0 : 1 ;

0 1 : 1 ;

1 0 : 1 ;

1 1 : 0 ;

endtable

endprimitive

如上一节所阐述,端口列表和声明部分可以改为:

primitive nand_my

(

output out ,

input a , b ) ;

......

endprimitive

output out ,

input a , b ) ;

......

endprimitive

状态表项

表示组合逻辑的状态表中的每一行的语法格式如下:

<input1> <input2> ... <inputN> : <output> ;

- 1、状态表中的 input 信号顺序要与 UDP 端口列表的顺序一致。

- 2、输入和输出用冒号 : 隔开。

- 3、状态表的每一行以分号 ; 结束。

- 4、能够产生确定输出值的所有输入项的组合都必须在状态表中列出,否则会输出 x 值。

例如在上述 UDP nand_my 中,如果 a=0, b=x,则输出 out = x ,因为该组合选项在 table 中无法找到。所以在编写 UDP 时,要完整的考虑输入的所有组合情况。

UDP nand_my 的状态表可以修改为:

table

//a b : out ;

0 0 : 1 ;

0 1 : 1 ;

1 0 : 1 ;

1 1 : 0 ;

0 x : 1 ;

x 0 : 1 ;

endtable

//a b : out ;

0 0 : 1 ;

0 1 : 1 ;

1 0 : 1 ;

1 1 : 0 ;

0 x : 1 ;

x 0 : 1 ;

endtable

无关项

UDP nand_my 中,当 a 或 b 两个输入只要有一个为 0 时,则输出为 1。

不影响输出结果的输入信号为无关项,可以用问号"?"来表示。状态表中的"?"项将自动展开为 0, 1 或 x。

因此 UDP nand_my 的状态表可以改为:

table

//a b : out ;

0 ? : 1 ;

? 0 : 1 ;

1 1 : 0 ;

//下面组合将输出 x,所以也可以省略,Verilog 默认会输出 x

1 x : x ;

x 1 : x ;

endtable

//a b : out ;

0 ? : 1 ;

? 0 : 1 ;

1 1 : 0 ;

//下面组合将输出 x,所以也可以省略,Verilog 默认会输出 x

1 x : x ;

x 1 : x ;

endtable

UDP 例化

UDP 调用格式与内置门级原语完全一致。

利用上述 UDP nand_my 完成《1.3 门延迟》中 D 触发器的仿真。

去除延迟信息,D 触发器模型如下。

实例

module D_TRI

(

input D , CP ,

output Q , QR ) ;

//part1, not gate

wire CPN , DN ;

not (CPN , CP ) ;

not (DN , D ) ;

//part2, master trigger

wire G3O , G4O ;

nand_my (G3O , D , CP ) ;

nand_my (G4O , DN , CP ) ;

wire G1O , G2O ;

nand_my (G1O , G3O , G2O ) ;

nand_my (G2O , G4O , G1O ) ;

//part3, slave trigger

wire G7O , G8O ;

nand_my (G7O , G1O , CPN ) ;

nand_my (G8O , G2O , CPN ) ;

wire G5O , G6O ;

nand_my (G5O , G7O , G6O ) ;

nand_my (G6O , G8O , G5O ) ;

assign Q = G5O ;

assign QR = G6O ;

endmodule

input D , CP ,

output Q , QR ) ;

//part1, not gate

wire CPN , DN ;

not (CPN , CP ) ;

not (DN , D ) ;

//part2, master trigger

wire G3O , G4O ;

nand_my (G3O , D , CP ) ;

nand_my (G4O , DN , CP ) ;

wire G1O , G2O ;

nand_my (G1O , G3O , G2O ) ;

nand_my (G2O , G4O , G1O ) ;

//part3, slave trigger

wire G7O , G8O ;

nand_my (G7O , G1O , CPN ) ;

nand_my (G8O , G2O , CPN ) ;

wire G5O , G6O ;

nand_my (G5O , G7O , G6O ) ;

nand_my (G6O , G8O , G5O ) ;

assign Q = G5O ;

assign QR = G6O ;

endmodule

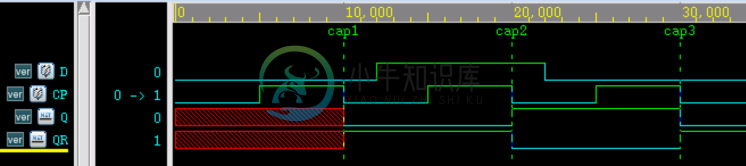

testbench 保持不变,仿真结果如下。

由图可知,触发器在时钟 CP 下降沿采集到了 D 端信号,并传递给 Q/QR ,在单周期内保持不变。

UDP 完成的与非门功能正确。

本章节源码下载

Download