Verilator 是一个高性能 Verilog HDL 模拟器与 lint 系统,用户编写一个小的 C++/SystemC 封装文件,该文件实例化用户顶层模块的“Verilate 化”模型。然后,这些 C++/SystemC 文件由 C++ 编译器(gcc/clang/MSVC++)进行编译,最终生成的可执行文件执行设计模拟。

Verilator 不会简单地将 Verilog HDL 转换为 C++ 或 SystemC。Verilator 不仅可以翻译,还可以将代码编译为速度更快的优化与可选的线程分区模型,同时这些模型封装在 C++/SystemC/Python 模块中。

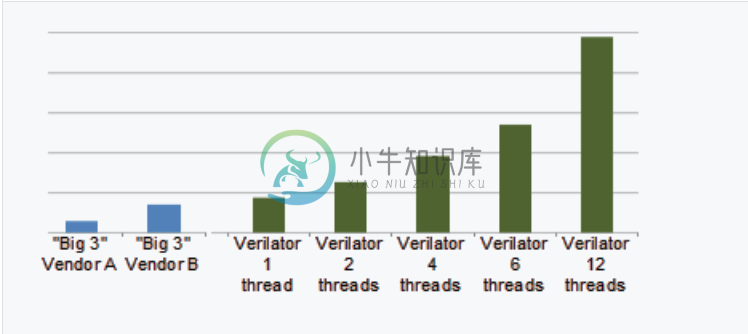

经过编译的 Verilog 模型,即使在单线程上执行的速度也比独立 SystemC 快 10 倍以上,并且在单线程上的执行速度比诸如 Icarus Verilog 之类的解释 Verilog 模拟器快 100 倍。多线程可能还会使速度提高 2-10 倍(在解释型模拟器上总共可以提高 200-1000 倍)。

-

本节将介绍下verilator所用到的主要数据结构。 AstNode AstNode类: class AstNode VL_NOT_FINAL { // v ASTNODE_PREFETCH depends on below ordering of members AstNode* m_nextp = nullptr; // Next peer in the parent's l

-

verilator最新已经升级到到了5.005,新版本的verilator在功能上更加完善,加入对Semantic Scheduling算法标准的支持,但因此效率肯定会有所损失,本节将接上一节测试最新版本性能变化,首先测试原始版本verilator的性能,我们先看下目前的verilator版本,输入: verilator --version 结果如下: Verilator 4.220 2022-0

-

之前的相关章节对verilator的相关功能和基本数据结构进行了介绍,本节将介绍如何使用verilator编译和仿真一个大一点的工程,将以阿里的玄铁为例来介绍,如何使用verilator对玄铁进行仿真。这里使用ubuntu20系统,且默认已经安装了verilator,如果还没有成功安装,可以参考安装与测试。 首先,我们从git上拷贝玄铁代码到本地: git clone https://github

-

本文请读者【直接关闭】,我后面的实践结果似乎和本文的实践结果不一样,真是见鬼了!我不知道发生了什么,还没有来得及进一步校验! 在其他文件不变的前提下,如果即将生成的mk文件和已有的mk文件不一样,就更新全部的源文件 这个事情说起来就有点诡异了,我们解释一下 我们只使用--exe,完成到生成全部的源文件,以及获取生成可执行文件的makefile文件这一步 编译的命令保持不变,例如 verilator

-

多线程模式 在多线程模式里,直到V3Order之前,Verilator Pipeline的前端(front end)是串行的模式。V3Order会建立一个细粒度语句级的依赖图(dependency graph),其通过单个的函数eval()来控制代码执行顺序。在串行模式下,通过依赖图将所有语句转化为一个完整的串行序。并行模式下,同一个依赖图是一个partitioner(V3Partition)的开

-

预学习阶段 verilator语法学习 常用网站: OJ刷题网站 HDL基础知识 verilator官网 定义一个模块 module name(varible, ...); // 定义一个模块 // 模块逻辑 endmodule // 模块结束 输入标识符:input,输出标识符:output module name( input a,b, output c,d );

-

1. 已有文件 已知our_OnOff.v和main.cpp文件,编写Makefile文件,在verilator软件仿真 our_OnOff.v module our_OnOff(a,b,f); input a; input b; output f; assign f = a ^ b; endmodule main.cpp #include "verilated_vcd_c.h

-

杂七杂八,都是网上搜集到的例子,对于Verilator一窍不通 希望能够通过这些对自己有个补充作用 若有冒犯请见谅,侵权删除 Verilator官方所给手册 C++例子 mkdir test_our //创建文件夹 cd test_our cat >our.v <<'EOF' module our; # 定义一个module initial # 定义一个initial块

-

verilog代码: module multi_logic (a,b,c,d,e,f,g,h,clk,ou1,ou2,ou3,ou4); input a,b,c,d,e,f,g,h,clk; output ou1,ou2,ou3,ou4; reg a,b,c,d,e,f,g,h,clk,ou1,ou2,ou3,ou4; always @(posedge c

-

verilog文件:multi_logic.v module multi_logic (a,clk,ou1); input a,clk; output ou1; reg a, clk, ou1; always @(posedge clk) begin ou1 <= a; end endmodule cpp文件:test_main.cpp #incl

-

一般来说,原生系统比docker容器快多少?

-

本文向大家介绍为何说虚拟DOM会提高性能?相关面试题,主要包含被问及为何说虚拟DOM会提高性能?时的应答技巧和注意事项,需要的朋友参考一下 虚拟dom相当于在js和真实dom中间加了一个缓存,利用dom diff算法避免了没有必要的dom操作,从而提高性能

-

本文向大家介绍为什么虚拟dom会提高性能?相关面试题,主要包含被问及为什么虚拟dom会提高性能?时的应答技巧和注意事项,需要的朋友参考一下 虚拟dom相当于在js和真实dom中间加了一个缓存,利用dom diff算法避免了没有必要的dom操作,从而提髙性能。 具体实现步骤如下: 1. 用JavaScript对象结构表示DOM树的结构;然后用这个树构建一个真正的DOM树,插到文档当中 2.当状态变更

-

升级flutter后,iOS模拟器的性能变得如此糟糕。例如,启动慢,显示键盘慢。 我查了颤振医生。这是我的结果。

-

有什么方法可以让Android模拟器运行除普通Android之外的系统映像吗?我正在开发一个应用程序,它在仿真器、华为和摩托罗拉的实体设备上运行良好,但在三星Galaxy S7上遇到了一些奇怪的问题。 既然我没有Galaxy S7的物理访问权限,那么有没有办法运行一个真正运行三星官方ROM的模拟器呢?注意,我说的不是一个模拟器皮肤,我说的是实际的系统映像。

-

问题内容: 我在Python中使用时遇到了一些困难: 测试实际上返回正确的值,但它是Mock对象,不是。您如何在Python库中模拟属性? 问题答案: 您需要使用和: 这意味着:调用时,在该调用的返回值上,为属性设置a以返回value 。